Table of Contents

Front-end manufacturing concepts and process flow

Semiconductor manufacturing is among the most complex processes on Earth, if not the most complex. Summarizing the process flow of such an industry in simple terms is difficult given the specific requirements of each type of product produced.

Here, we divide the manufacturing processes into four parts:

- wafer fabrication

- photomask fabrication

- front-end processes

- back-end processes

Fab production

These processes take place in specialized factories called “fabs.” Most of the time, fabs operate at an average utilization rate of 80%. The manufacturing process involves hundreds of highly sophisticated machines across hundreds of steps—and in some cases, more than 1,000 steps for the most advanced products. According to the Semiconductor Industry Association (SIA), it takes up to 26 weeks to produce a finished chip (front-end processes). The assembly, testing, and packaging stages take an average of 6 weeks (back-end processes).

All the manufacturing processes involved in creating a finished semiconductor wafer, froms start to finish, are referred to as the cycle time. The cycle time is defined my Little's Law, i.e. average inventory (WIP) = throughput time (also called cycle time) x throughput rate. The WIP inventory represents the queue lenght (how many products are being processed at the moment?). The throughput time represents the time in queue (how much time does my product stay in queue?). The throughput rate represents the amount of products processed by unit of time (1 day, 1 week, etc.). For instance, if the throughput time is 10 weeks and the rate 7,000 wafers/week, then the WIP will be 70,000 wafers. Increasing productivity in a fab is determined by these three factors (WIP inventory, throughput rate and time). Note also that the throughput rate depends of the number of steps. Generally speaking, the more advanced the processes are, the higher the throughput rate.

Generally, the most common metric for cycle time in the fab is “days per mask layer”. A “mask layer” includes all of the sequential process recipes (steps) required to manufacture the product up to the next photolithographic step in the process.

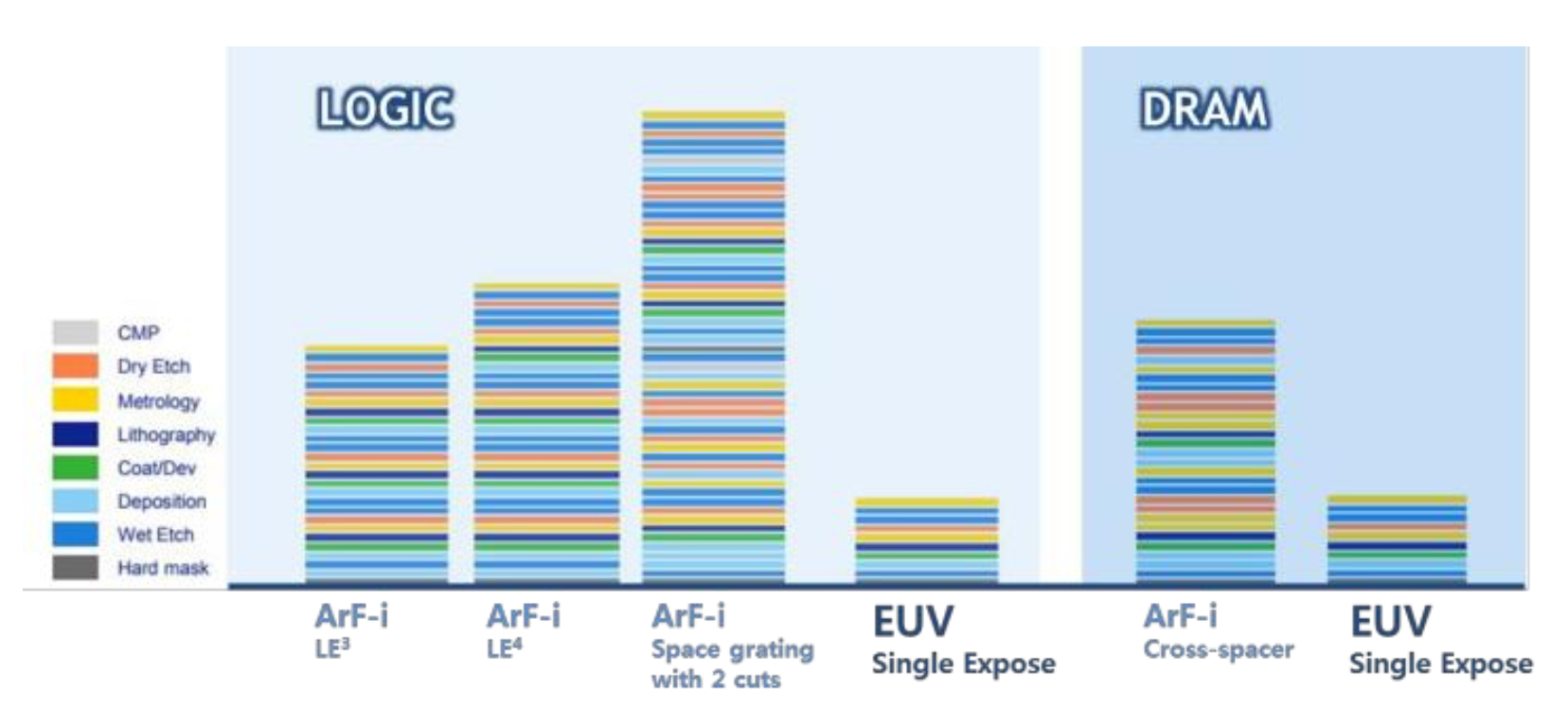

The number of layers in a semiconductor chip has a direct impact on its manufacturing cycle time. Chips with higher layer counts require more intricate patterning and deposition processes, which consequently extends the overall manufacturing timeline. For instance, advanced processors designed for high-performance computing or artificial intelligence applications typically have more layers, thus longer cycle times compared to simpler chips like microcontrollers. According to the Electronic Components Industry Association, a 28nm device may have 40 to 50 mask layers ; a 14nm/10nm device has 60 layers ; 7nm 80 to 85 ; a 5nm device could have 100 layers. Generally, the most common metric for cycle time in the fab is “days per mask layer”. So, using DUV lithographic techniques, the cycle times are increasing from roughly 40 days at 28nm, to 60 days at 14nm/10nm, to 80 to 85 days at 7nm. 5nm may extend to 100 days (without extreme ultraviolet (EUV) lithography). Furthermore, cycle time is generally longer when a new process is implemented, but decreases as the process matures.

Another challenge to manage is that as throughput approaches the machines’ maximum effective capacity, cycle time increases, as Martin described in 1999. This is due to the varying idle times between machines—specifically, those capable of handling batches versus those that can only process one or a few wafers at a time.

New advanced nodes (logic and memory) put an additional strain on fab production. According to SEMI : “since 2020, fab cycle times have grown at a compound annual growth rate of 14.8%. This represents a fundamental deceleration in fab throughput, meaning that even with the same number of tools and consistent utilization rates, the volume of wafers that can be processed is now structurally constrained.” They point this growth to “rising process complexity, increased equipment density, and tighter quality control requirements” (equipment spending per wafer area has surged over 150% since 2020). In the case of advanced memory, SEMI notes that “HBM wafers consume over three times more wafer area per bit compared to standard DRAM, creating potentially significant wafer demand.”

Sources

- Mönch, L., Fowler, J. W., & Mason, S. J. (2012). Production planning and control for semiconductor wafer fabrication facilities: modeling, analysis, and systems. Springer Science & Business Media.

- Micron. (2026). An application of Little's Law in Micron’s supply chain.

- Martin, D. P. (1999, September). Total operational efficiency (TOE): the determination of two capacity and cycle time components and their relationship to productivity improvements in a semiconductor manufacturing line. In 10th Annual IEEE/SEMI. Advanced Semiconductor Manufacturing Conference and Workshop. ASMC 99 Proceedings (Cat. No. 99CH36295) (pp. 37-41). IEEE.

- Ibrahim, K., Chik, M., & Hashim, U. (2016). Semiconductor Fabrication Strategy for Cycle Time and Capacity Optimization: Past and Present. In Proceedings of the 2016 International Conference on Industrial Engineering and Operations Management (No. 1, pp. 2798-2807).

- Wartelle, A., Dauzère-Pérès, S., Yugma, C., Christ, Q., & Roussel, R. (2025, August). Forecasting Wafer Fab Outputs using Lot Remaining Cycle Time Prediction in Semiconductor Manufacturing. In 2025 IEEE 21st International Conference on Automation Science and Engineering (CASE) (pp. 911-914). IEEE.

- Ezici, B., Costa, P., & Xu, J. (2022). Workflow Modeling and Simulation Analysis for Semiconductor Wafer Fab Manufacturing. In IISE Annual Conference. Proceedings (pp. 1-6). Institute of Industrial and Systems Engineers (IISE).

- Semiconductor Industry Association. (2021). Chipmakers Are Ramping Up Production to Address Semiconductor Shortage. Here’s Why that Takes Time

- Electronic Components Industry Association. (2023). Understanding Lead Times

- Lapedus, M. (2017). Battling Fab Cycle Times, Semiconductor Engineering.

- Yoon, S. (2025). From Latency to Reaction: Simulating the Next Wafer Demand Inflection, SEMI.

Yield modelling

In addition to the various constraints on productivity, yields are another factor to consider. But 'yield' can refer to many different aspects of the manufacturing process.

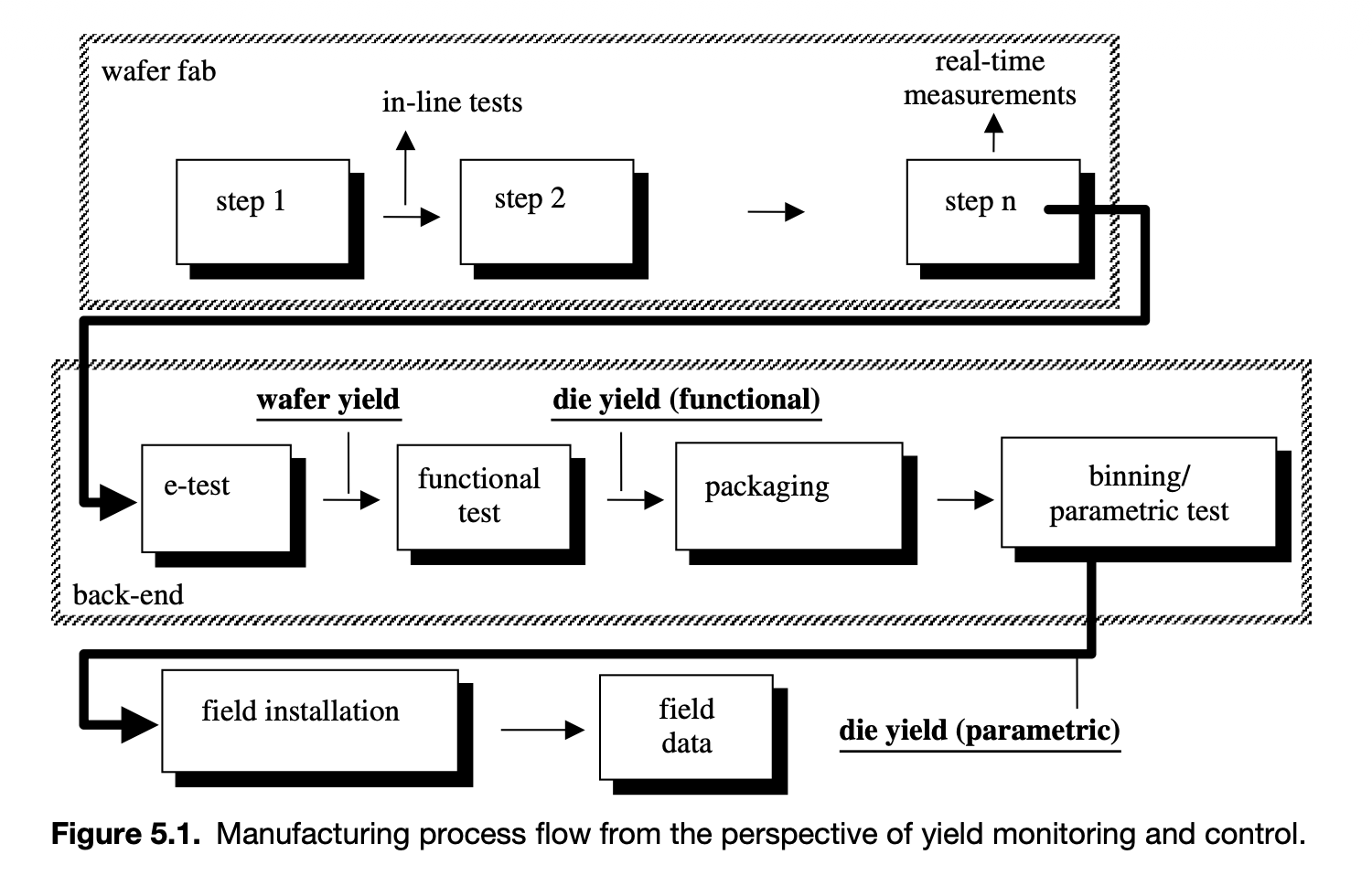

According to May & Spanos, the most basic definition, is that of manufacturing yield. This figure 'measures the proportion of successfully fabricated products compared to the number that have started the process'. Wafer yield refers to wafer that get scrapped along the manufacturing process because of equipment malfunctioning, wafer transport problems, etc. Wafer yield can be measured in three ways:

- Wafer yield – the percentage of wafers that make it to final probing ;

- Probe testing yield –the percentage of wafers that make it through the probe testing steps ;

- Final testing yield – the percentage of wafers that make it through the final electrical testing step.

Once a wafer successfully passed this final test, the die can be tested and define the design yield. This yield has two components:

- Functional yield (also known as “hard” or “catastrophic” yield) – the proportion of fully functional ICs ;

- Parametric yield (also known as “soft” yield) * the overall performance achieved by the functional ICs.

The functional yield test is runned before dicing in order to avoid packaging and shipping of a defective die. The parametric yield is defined after dicing, the dies will then be separated into various performance “bins” depending of parametric variation.

The figure below from May & Spanos summarized the different yield calculation steps.

Sources

- May, G. S., & Spanos, C. J. (2006). Fundamentals of semiconductor manufacturing and process control. John Wiley & Sons.

Front-end process flow

Front-end process flow varies widely depending on the target technology nodes and the type of device (logic, memory, etc.). The processes follow a general sequence for each mask: deposition, lithography, etching, doping, resist stripping, and metallization. Each step may be interspersed with intermediate cleaning and inspection steps.

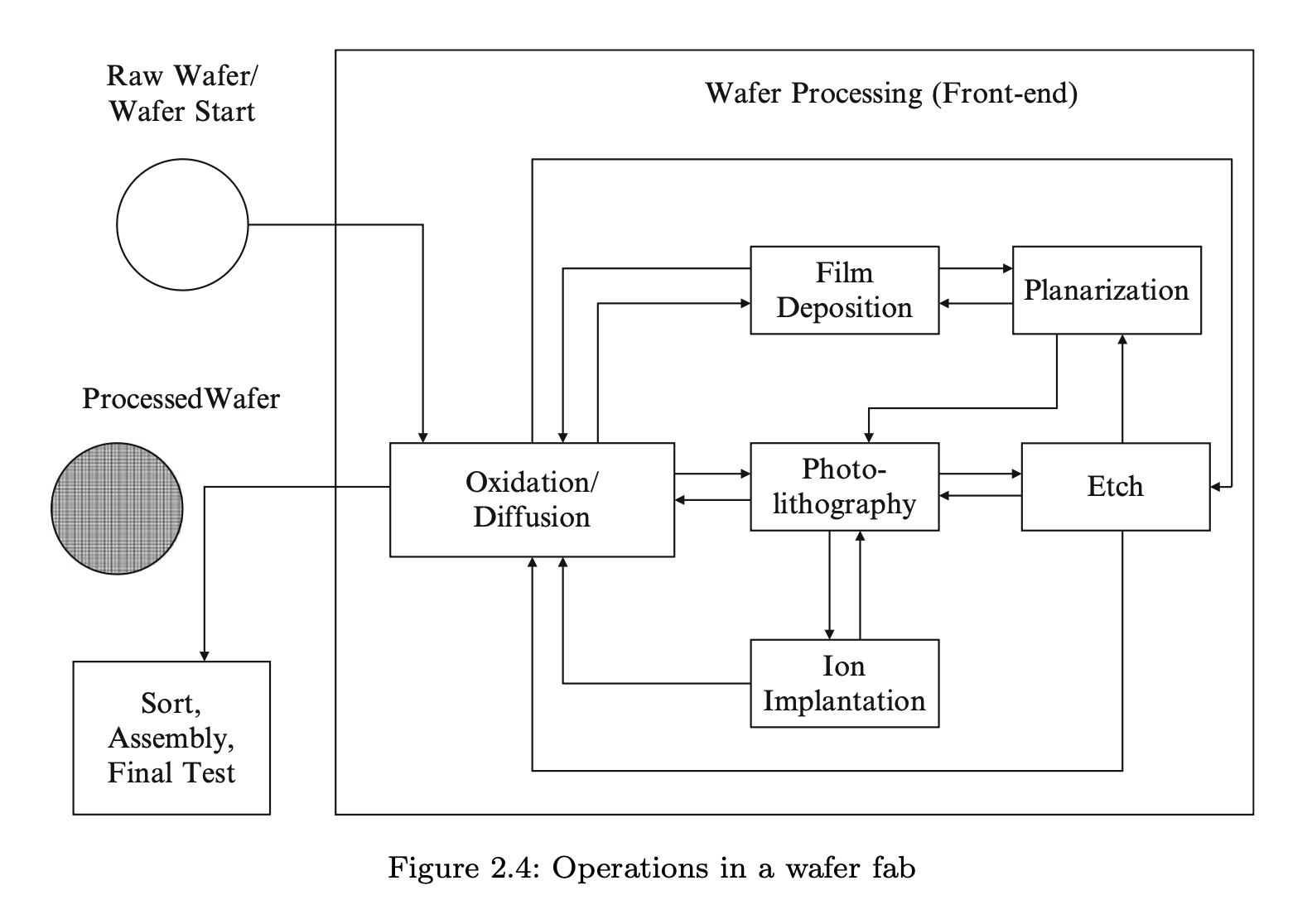

The process flow can be summarized in different ways. From a fab operations perspective, Mönch et al provide a simple view of the looping dynamics on front-end processes.

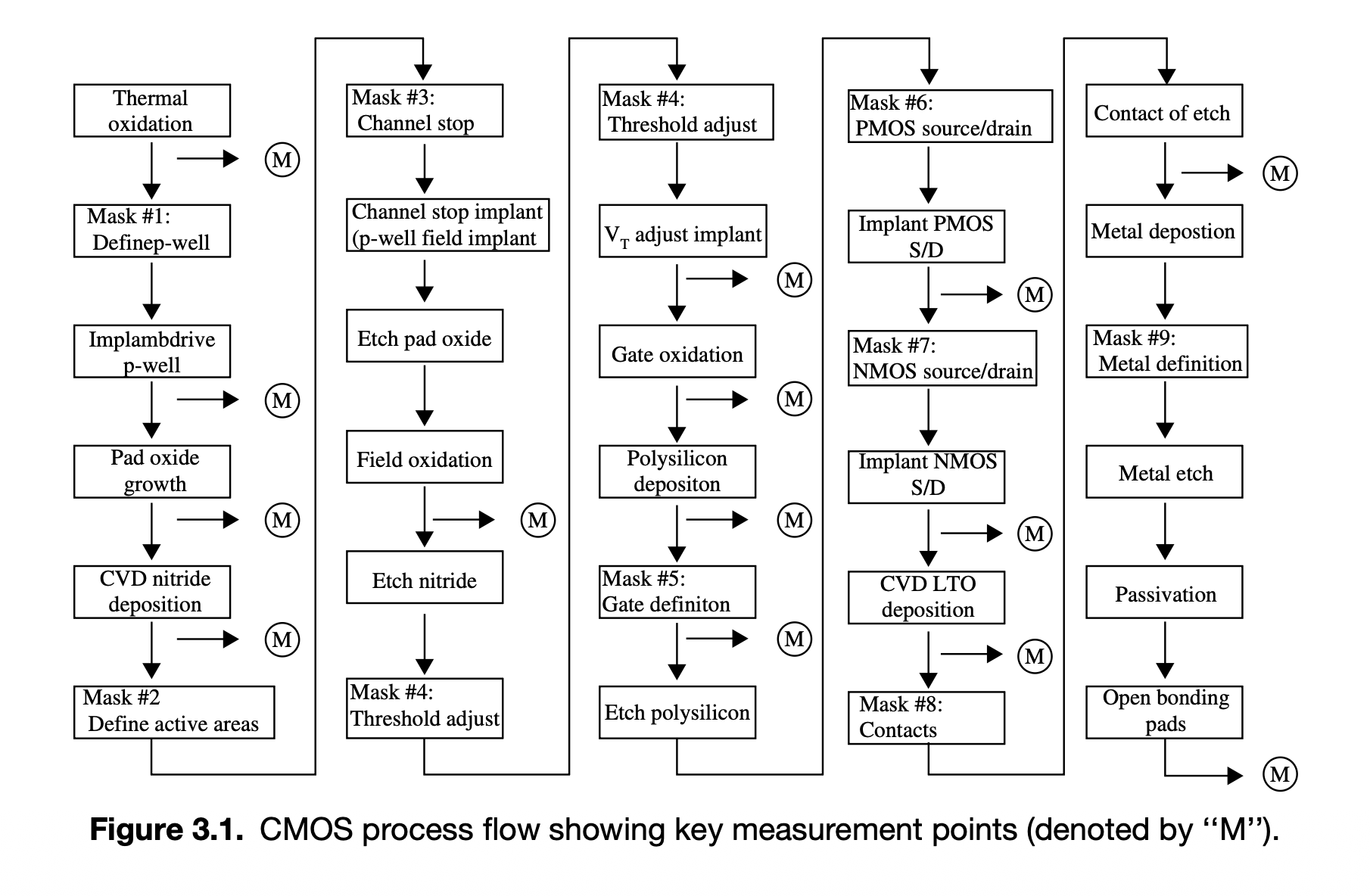

May and Spanos propose a simplified process flow for a planar CMOS, a simpler flow compared to today's 3D structures.

Going deeper, Plummer et al decompose all the sub-steps that go into a photoresist deposition step for an old manufacturing process. On a more technical view, Franssila shows what happens in an epitaxy reactor, including sub-steps timing and temperature variation.

On more recent technology nodes, Jung shows the different steps depending of patterning techniques for logic and DRAM devices. The looping sequences are particulary visible here and shows the complexity depending of selected processes.

Sources

- Mönch, L., Fowler, J. W., & Mason, S. J. (2012). Production planning and control for semiconductor wafer fabrication facilities: modeling, analysis, and systems. Springer Science & Business Media.

- May, G. S., & Spanos, C. J. (2006). Fundamentals of semiconductor manufacturing and process control. John Wiley & Sons.

- Plummer, J. D. (2009). Silicon VLSI technology: fundamentals, practice and modeling. Pearson Education India.

- Franssila, S. (2010). Introduction to microfabrication. John Wiley & Sons.

- Jung, E. S. (2018, December). 4 th Industrial Revolution and Boundry: Challenges and Opportunities. In 2018 IEEE International Electron Devices Meeting (IEDM) (pp. 1-1). IEEE.

Full process flow for memory devices

Xiao provides the most detailed description of the processes used to manufacture 3D DRAM and NAND devices. Such a detailed public explanation is rare to find and applies only to two types of devices for advanced technology nodes. Nevertheless, it provides a detailed understanding of the various process loops for each mask.

Process flow for 3D devices on DRAM

AA Module

- Wafer clean

- Pad oxidation

- SiN hard mask deposition

- Amorphous silicon hard mask deposition

- AA mask 1

- Etch top hard mask

- PR strip/clean

- AA mask 2

- Etch bottom hard mask

- PR strip and clean

- Etch pad oxide

- Etch silicon trench

- Wafer clean

- Oxidation

- STI oxide CVD to fill the trench

- STI oxide CMP, stop on nitride

- Wet strip nitride and pad oxide

- Wafer clean

Well formation

- Sacrificial oxide growth

- Cell p-well mask

- P-well implantation

- N + S/D implantation

- PR removal and clean

- Peripheral n-well mask

- N-well implantation

- PMOS VT adjust implantation

- PR removal and clean

- Peripheral p-well mask

- P-well implantation

- NMOS VT adjust implantation

- Photoresist removal and clean

- Sacrificial oxide removal and clean

- Rapid thermal anneal

BWL module

- Wafer clean

- Oxidation

- Hard-mask deposition

- BWL mask

- Etch hard mask

- BWL trench etch

- PR strip & clean

- Oxidation

- W and TiN etch back

- Wafer clean

- Oxide deposition

- Oxide CMP

- Strip hard-mask

- Oxide deposition

- TiN gate electrode deposition

- W deposition

BLC module

- Wafer clean

- Peripheral mask

- Etch oxide

- PR strip/clean

- Gate oxidation and nitridation

- Polysilicon deposition

- Wafer clean

- PMOS poly-dope mask

- PMOS poly implantation

- PR strip/clean

- Array area mask

- Etch polysilicon

- PR strip/clean

- BLC mask

- Etch oxide

- PR strip clean

- Polysilicon deposition

- TiN and W deposition

- SiN deposition

BL and peripheral transistor module

- Wafer clean

- BL mask

- BL and peripheral gate etch

- PR strip/clean/ACI

- Re-oxidation

- Peripheral NMOS SDE mask

- Peripheral NMOS SDE implantation

- PR strip/clean

- Peripheral PMOS SDE mask

- Peripheral PMOS SDE implantation

- PR strip/clean

- Spacer dielectric film deposition

- Spacer film etch back

- Peripheral NMOS SD mask

- Peripheral NMOS SD implantation

- PR strip/clean

- Peripheral PMOS SD mask

- Peripheral PMOS SD implantation

- PR strip/clean

- RTA

SNC, peripheral contact, and M1 process steps

- ILD1 deposition

- LD1 CMP

- HM deposition

- SNC mask 1

- Etch HM

- PR strip/clean

- SNC mask 2

- Etch HM

- PR strip/clean

- Etch ILD1

- Wafer clean

- Ti/TiN/W deposition

- W/TiN/Ti CMP

- Etch stop layer deposition

- ILD2 deposition

- M1 mask

- Etch ILD2

- PR strip/clean

- Ti/TiN/W deposition

- W/TiN/Ti CMP

SN module

- Wafer clean

- Each stop layer (ESL) deposition

- ILD deposition

- SiN deposition

- SN mask 1

- Etch nitride

- PR strip/clean

- SN mask 2

- Etch nitride

- PR strip/clean

- Etch oxide

- TiN deposition

- PR coating

- RP etch back

- TiN etch

- SiN slot mask

- Nitride etch

- PR strip/clean

- ILD removal

- Wafer clean

- High-k film deposition

- TiN and conducting filler deposition

V1 and M2 process steps

- Peripheral area mask

- Etch SiGe/TiN/ZAZ

- PR strip/clean

- ILD3 deposition

- ILD3 CMP

- V1 mask

- V1 etch

- PR strip and clean

- Ti/TiN deposition

- W deposition

- W/TiN/Ti CMP

- ESL deposition

- ILD4 deposition

- M2 mask

- M2 etch

- PR strip and clean

- Barrier and seed-layer deposition

- Bulk copper plating

- Cu anneal

- Cu CMP

V2 and M3 process steps

- ESL, ILD5, and dielectric cap deposition

- Metal HM deposition

- M3 mask

- HM etch

- PR strip and clean

- V2 mask

- Dielectric cap and ILD5 etch

- PR strip and clean

- ILD 5 etch

- ESL removal

- Clean

- Barrier and seed-layer deposition

- Bulk copper plating

- Cu anneal

- Cu CMP

V3-M4 and passivation process steps

- ESL and ILD6 deposition

- V3 mask

- ILD6 and ESL etch

- Pr strip and clean

- Ti/TiN/W deposition

- W/TiN/Ti CMP

- Wafer clean

- Ti/Al-Cu/TiN deposition

- M4 mask

- Etch TiN/Al-Cu/Ti stack

- PR strip and clean

- Passivation oxide and nitride deposition

- Bond pad mask

- Etch nitride and oxide

- PR strip and clean

Process flow for 3D-NAND Flash

Peripheral CMOS process steps

- Wafer clean

- Pad oxidation

- Nitride deposition

- AA mask

- Nitride etch

- PR strip and clean

- Silicon etch

- Wafer clean

- Oxidation

- Oxide deposition

- Oxide CMP

- Strip nitride and pad oxide and wafer clean

- Oxidation of sacrificial oxide

- n-well mask

- n-well and p-channel ion implantation

- PR strip and clean

- Strip sacrificial oxide and wafer clean

- Gate oxidation

- PolySi and silicide deposition

- Poly-dope mask

- Poly-dope ion implantation

- PR strip and clean

- Hard mask deposition

- Gate mask

- Etch hard mask

- PR strip and clean

- Etch silicide/polySi

- Wafer clean

- n-LDD mask

- n-LDD ion implantation

- PR strip and clean

- p-LDD mask

- p-LDD ion implantation

- PR strip and clean

- Spacer dielectric film CVD

- Dielectric etch back

- n-S/D mask

- n-S/D ion implantation

- PR strip and clean

- p-S/D mask

- p-S/D ion implantation

- PR strip and clean

- RTA

- SiN liner deposition

- PMD deposition

Multi-layer-deposition and staircase-formation process step

- Array area mask

- Etch oxide and barrier nitride

- PR strip and clean

- CVD oxide 1, CVD Nitride 1 and lower SG nitride

- CVD oxide 2, CVD Nitride 2 and lower cell nitride

- CVD oxide 3, Nitride 3 pairs

- Repeating the process until Oxide N/Nitride N

- CVD Oxide N+1 and cap oxide

- First staircase mask

- Etch Oxide N+1/Nitride N, stop on Oxide N

- PR trimming

- Etch Oxide N/Nitride N-1, stop on Oxide N-1

- PR trimming

- Etch Oxide N-1/Nitride N-2, stop on Oxide N-2

- Repeating trimming and O/N pair etch

- PR strip and clean

- Second staircase mask

- Repeating trimming and O/N pair etch

- Third staircase mask

- Repeating trimming and O/N pair etch

- Etch Oxide 1, stop on silicon

- PR strip and wafer clean

- Oxide CVD

- Oxide CMP

3D NAND channel formation process steps

- Channel mask

- Etch hard mask

- Etch multi-layers

- Remove hard mask and wafer clean

- SEG Si

- Deposit high-k dielectric

- Deposit charge trap nitride

- Deposit gate oxide

- Etch back channel dielectric layers

- Wafer clean

- Deposit polySi channel

- Deposit silicon oxide filler

- Oxide recess

- Deposit polySi

- PolySi CMP

- Post-CMP clean

Process steps for the isolation module of 3D-NAND

- Wafer clean

- Isolation mask

- Etch hard mask

- Etch trenches in ONON multi-layers and stop on silicon

- Remove hard mask

- Remove nitride layers

- Wafer clean

- Oxidation of SEG

- TiN deposition

- W deposition

- Trench W removal

- Trench TiN removal

- Wafer clean

- Oxide deposition

- Oxide etch back

- TiN deposition

- W deposition

- W CMP

- Oxide cap deposition

Process steps of the contact and interconnect module of 3D-NAND

- Wafer clean

- First contact mask

- Etch hard mask

- Etch shallower staircase contacts

- Strip PR and wafer clean

- Apply the second contact mask and etch staircase contacts

- Strip PR and wafer clean

- Repeating staircase contact litho, etch and clean

- Remove hard mask and wafer clean

- TiN liner deposition

- W deposition

- W CMP

- Wafer clean

- Oxide CVD

- V1 mask

- V1 etch, PR strip, and clean

- Oxide CVD

- M1 mask

- M1 etch, PR strip, and clean

- TiN deposition, W CVD and W CMP

- Oxide CVD

- V2 mask

- V2 etch, PR strip, and clean

- TiN deposition, W CVD, W CMP

- Oxide CVD

- M2 mask

- M2 etch, PR strip, and clean

- TaN deposition, Cu seed deposition, Cu plating, Cu anneal and Cu CMP

- Oxide CVD

- V3 mask

- V3 etch, PR strip, and clean

- TiN deposition, W CVD, W CMP

- PVD TiN, PVD Al-Cu and PVD TiN

- M3 mask

- M3 etch TiN/W/TiN metal stack, PR strip and clean

- Oxide CVD and nitride CVD

- Bond pad mask

- Etch nitride/oxide

- PR strip and clean

Sources

- Xiao, H. (2016). 3D IC Devices, Technologies, and Manufacturing. SPIE press.

Discussion